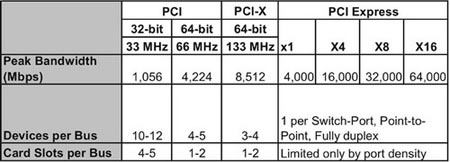

Table 1 Comparison of PCI Standards

A pair of transmit and receive channels that work at the same time is called a path. The transmit and receive channels use the Low Voltage Differential Signaling (LVDS) standard to transmit data. The data clock is embedded in each channel to achieve a very high data rate.

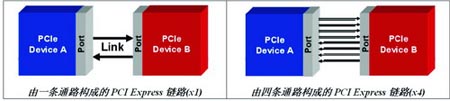

Figure 1 PCI Express link

A PCI Express link consists of multiple lanes. Adding more lanes in the link can increase the bandwidth of the PCI Express link. There are four types of link lane bandwidth supported by the specification: x1, x4, x8, and x16.

PCI Express Advanced Features

Active power management: In PCI Express, the bus interface always operates regardless of signal transmission on the bus. In the idle state, when there is no operation on the bus, this leads to high power consumption. To reduce power consumption, PCI Express provides active power management mechanisms to reduce power consumption when the bus is idle.

Real-time data traffic: PCI Express guarantees that the packet arrives at its destination within a given time of the virtual channel, implementing different levels of quality of service (QoS).

Hot-swappable: PCI Express supports hot-plugging while the system is operating, reducing system downtime during system upgrade and commissioning.

Error Detection and Correction: Due to the cyclic redundancy check (CRC) function at the data link layer, PCI Express can better check data integrity, perform error handling, improve bus operation reliability, and enhance data recovery. ability.

Difficulties in Implementing PCI Express Interfaces

Using custom logic to implement the PCI Express interface in dedicated products has many difficulties:

Adaptive Hardware: The hardware platform selected for the design of a specific product must be able to meet the electrical specifications and performance requirements of the PCI Express protocol. In typical PCI Express terminal applications such as memory, servers, and backplanes, PC-based networks are rapidly growing in bandwidth requirements and data rates. Such products also need to be flexibly adapted to new standards that may replace existing standards.

System Performance: Since the expected data rate of the PCI Express link is in the Gbps range, the timing margin is very tight. Implementing any PCI Express interface must meet the strict performance requirements of the system.

Reliability: To implement this protocol, it must be ensured that the product has a reliable performance within the range of possible operating voltage and temperature (PVT) variations.

Versatility: The PCI Express interface is often used to connect different semiconductor devices. Therefore, the products of this agreement must be compatible with other PCI Express devices on the market.

Easy to use: For system designers, PCI Express should be simple to implement (or in other words, open the package). This typically refers to a reference design, a user-friendly software tool, a prototyping platform for verifying the design, and complete documentation.

PCI Express Interface in FPGA

FPGAs are often used to bridge devices that use different protocols. Moreover, due to the increase in the capacity of logic gates, the richness of system-level features, and the increase in system throughput, FPGAs have also gradually assumed the core functions of the system.

In recent years, FPGA vendors have begun to implement high-speed, high-speed serial I/O interfaces using hardware IP such as Gigabit transceiver modules. For example, Altera's Stratix II GX FPGAs have data rates of up to 6.375 Gbps per channel. With the Gigabit Transceiver Module, high-speed serial protocols can now be implemented in a single FPGA, including Gigabit Ethernet, Serial Rapid IO, PCI Express, XAUI, and HD-SDI.

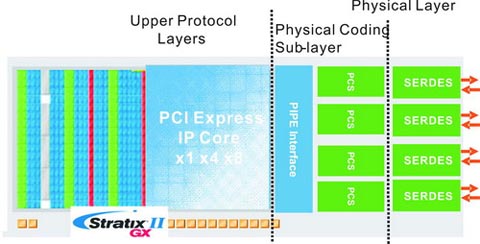

Gigabit transceiver modules typically include a physical layer and a physical coding sublayer (PCS) as shown in FIG. The upper layer protocol is implemented in the FPGA architecture using IP written in hardware description language (HDL).

Figure 2 PCI Express High Speed ​​Serial I/O

FPGA's PCI Express interface has obvious advantages:

Flexibility: Because the FPGA fabric is inherently programmable, any product that uses an FPGA has a lot of flexibility in terms of the number of channels, the features, the possibilities for implementing custom hardware, and the connection to other semiconductor devices.

Easy to update: Products using FPGAs can adapt to changes in protocol and functional requirements. Therefore, this type of product can be outdated and easily updated.

Performance is mature: Gigabit transceiver modules in FPGAs guarantee timing slack. The PCI Express eye diagram in Figure 3 has been verified to comply with the PCI-SIG standard. This means that users can be assured of product compatibility even before starting the design.

Figure 3 PCI Express Interface in Stratix II GX Complies with PCI-SIG

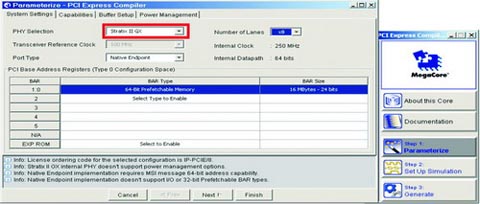

Easy to use: FPGA vendors also provide development boards, reference designs, and design guidelines that reduce the difficulty of implementing PCI Express interfaces. For example, Altera provides an interface-friendly PCI compiler tool that makes it easy to customize, build, and test multi-lane PCI Express interfaces in Stratix II GX FPGAs (Figure 4).

Figure 4 Easy-to-use PCI compiler software tools

Versatility: Stratix II GX FPGAs are successfully tested for commonality with other PCI Express-compatible devices, such as the Freescale PowerQUICC III processor.

With Gigabit transceivers integrated in FPGAs, high-speed system designers who previously used discrete transceiver chips can now take full advantage of the flexibility of FPGAs and the time-to-market advantages of their products, and focus on creating higher performance and reducing risk. At the same time, they are also able to respond to changes in demand on the market in a timely manner.

Sdec 21-75Kw Diesel Generator,Sdec Portable Power Generator,Sdec Open Type Power Generator,Sdec Container Power Generator

Shanghai Kosta Electric Co., Ltd. , https://www.generatorkosta.com