First, the semiconductor industry eco-environment The semiconductor industry was born in the 70s of the last century. At that time, it was mainly driven by two major factors: one was to provide more cost-effective memory for the computer industry, and the second was to meet the needs of companies developing new products with specific functions. Integrated circuits for production.

By the 1980s, system specifications were firmly in the hands of system integrators. Memory devices are updated every 3 years and then used by logic device manufacturers.

In the 1990s, logic device integrated circuit manufacturers accelerated the introduction of new technologies to update at a rate of 2 generations per year, immediately following the memory vendors. The unusually strong correlation between technological advancement and product performance enhancements has led to a considerable portion of the control of system performance and profit to integrated circuit (IC) manufacturers. They take advantage of this new balance of power, so that the entire semiconductor industry revenue during this period average annual growth rate of 17%.

In the first decade of the 21st century, a new ecological environment for the semiconductor industry has been formed:

First, a new generation of semiconductor technology every 2 years, resulting in integrated circuits and millions of transistors that can be produced with high efficiency and low cost, making it possible to integrate at a lower cost and on a chip or in the same package. system. In addition, advances in packaging technology have allowed us to place multiple chips in the same package. Such devices are defined as system on chip (SOC) and system in package (SIP).

The second is that integrated circuit foundries can provide "new generation of application-specific integrated circuits" again at a very attractive cost, which has led to a very profitable industry--integrated circuit design.

Thirdly, the advancement of integrated circuit high-end equipment has led to the development of neighboring technologies, which has greatly reduced the cost of flat panel displays, MEMS sensors, radio equipment, and passive devices. Under this condition, system integrators once again controlled system design and product integration.

Fourth, the rise of Internet applications and mobile smart terminals has led to the widespread deployment of fiber optic cables and the development of a variety of wireless technologies to achieve an unprecedented global mobile Internet. This ecosystem has created the emerging market of the "Internet of things", and innovative product manufacturers, telecommunications companies, data and information distributors and content providers are fighting for the market's dominance.

Semiconductors are the cornerstone of all of the aforementioned applications. All innovation cannot be separated from the support of the semiconductor industry.

Second, global semiconductor technology development route In the late 1960s, the invention of the silicon gate self-aligned process laid the foundation for semiconductor specifications. Moore's Law that Moore's transistor was updated every two years in 1965, and Dennard's Law proposed by Dennard in 1975, promoted the growth of the semiconductor industry until the beginning of the 21st century. This is a tradition. The Classical Geometrically Driven Scaling era. The basis for entering the Equivalent Scaling era is strained silicon, high-dielectric metal gates, multi-gate transistors, and compound semiconductors. The realization of these technologies supports the development of the semiconductor industry in the past decade and will continue. Support the development of future industries.

(1) Device information processing technology is pushing the semiconductor industry into wider application areas, and device cost and performance will continue to be closely related to the expansion of the dimensions and functions of Complementary Metal-Oxide-Semiconductor Transistor (CMOS).

Strained silicon, high-dielectric metal gates, and multi-gate transistors are now widely used in the manufacture of integrated circuits, and the focus of further enhancement of device performance will be on III-V elemental materials and germanium. Compared with silicon devices, these materials will enable the device to have higher mobility. In order to take advantage of a well-established silicon platform, it is expected that the new high-mobility materials will epitaxially grow on the silicon substrate.

2D Scaling will eventually reach its basic limits during the 2013 International Technology Roadmap for Semiconductors (ITRS), whether logic or storage devices are exploring how to use vertical dimensions (3D). The combination of 3D device architecture and low-power devices will open the "3D Power Scaling" era. The increase in the number of transistors per unit area will eventually be achieved through multilayer stack transistors.

Unfortunately, there is no new breakthrough in interconnects because there is no viable material with a lower resistivity than copper. However, progress in processing edgeless wrapped materials such as carbon nanotubes, graphene compositions, etc. provides the basis for the development of "ballistic conductors," which may emerge in the next decade.

Multi-chip three-dimensional packaging provides a possible route to reduce the interconnect resistance, mainly by increasing the conductor cross section (vertical) and reducing the length of each interconnection path.

However, the lateral dimension expansion of CMOS or the equivalent device currently being studied will eventually reach the limit. New opportunities for future semiconductor products include: first, the expansion of the CMOS platform through the heterogeneous integration of new technologies; and second, the development of devices that support the next generation of information processing paradigms.

(b) System Integration System integration has shifted from a data computing, personal computer-centric model to a highly diversified mobile communication model. Integrated circuit design is changing from the goal of performance driving to the goal of low-power consumption, enabling multiple technologies to be heterogeneously integrated in a limited space (such as GPS, phones, tablets, mobile phones, etc.), thus completely changing the semiconductor industry. . In short, performance was a unique goal in the past; today, the goal of minimizing power consumption leads to integrated circuit design.

System-on-chip and system-in-package products have become the main driving force in the semiconductor industry. In the past few years, the output of smart phones and tablets has exceeded the output of microprocessors. The basis of heterogeneous integration relies on the integration of the "More Moore (MM) device with the "More than Moore (MtM)" element.

For example, microelectromechanical systems (MEMS) devices are currently integrated into various types of systems such as automobiles, video projectors, tablet computers, smart phones, and gaming platforms. In general, MEMS devices add useful functionality to the system and enhance the core functionality of the system. For example, a MEMS accelerometer on a smartphone can detect the vertical orientation of the phone and rotate the image displayed on the screen. The user interface is improved through the additional features introduced by MEMS, but the phone can still operate without it. In contrast, video recorders and inkjet printers based on digital light projectors (DLP) will not work without MEMS devices. Multi-mode sensing technology has also become an integral part of mobile devices and has become a key driving force for the Internet of Things.

Rapid advances in digital data and connectivity technologies have revolutionized healthcare services. Silicon, MEMS, and optical sensing technologies are making this revolution possible.

Mobile phones can already provide a lot of health information. The accelerometer tracks movement and sleep, and the built-in light sensor senses the heart rate when the user touches the phone. The camera on the phone can be used for different purposes, such as checking the calorie content of food, or identifying their emotions based on facial expressions. Extensive mobile phone applications have evolved to analyze this data and feed it back to consumers in a way that is easy to understand and operate.

Looking at the development of equipment and systems in the next 7-15 years (after 2020), devices based on new principles will support a new architecture. For example, a spin wave device (SWD) is a kind of magnetic logic device that utilizes a collective rotary oscillation (spin wave) for information transmission and processing. The spin wave device converts the input voltage signal into a spin wave, calculates a spin wave, and converts the spin wave output into a voltage signal. In a single-core architecture, massively parallel data processing for multiple frequencies can be performed at very low power by creating different information channels for each frequency. In addition, some new devices promote the creation of new architectures. For example, storage-class memory (SCM) is a device that combines the advantages of solid-state memory (high performance and robustness), archiving capabilities, and the low cost of magnetic storage of conventional hard disks. Such a device requires a nonvolatile memory (NVM) technology that can create per-bit storage space at a very low cost.

(3) Manufacturing is driven by dimensions and the precision of integrated circuit manufacturing will reach several nanometers in the next 15 years. It has become more and more difficult to measure the physical characteristics on a wafer using any technique, and this task will basically be realized by associating process parameters and device parameters. By controlling equipment stability and process reproducibility, precise control of process parameters such as feature size can already be accomplished.

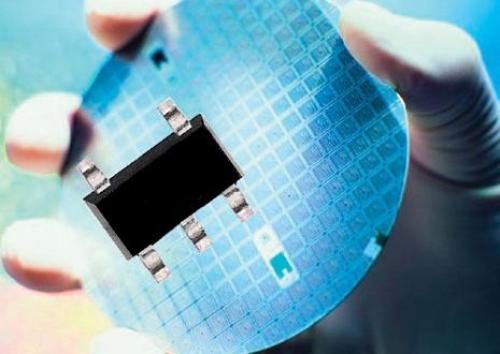

Fabs are continuously being driven by data, and the requirements for data volume, communication speed, data quality, availability, etc. are understood and quantified. Wafers face the challenge of transitioning from 300mm to 450mm. Focusing on the development of 300mm and 450mm common technologies, 450mm wafer fabs will benefit from improved technology for 300mm wafers.

System-on-chip and system-in-package integration will continue to heat up. The increase in integration drives the reintegration of test solutions to maintain test costs and product quality specifications. Optimized test solutions may need to access and test embedded modules and cores. The well-known chip (KGD) technology that provides high-quality die for multi-chip packaging has also become very important and has become an important part of the test technology and cost compromise.

III. Major Challenges (I) Short-Term Challenges (Now to 2020): Performance Improvements 1. The traditional extended path of logic device planar complementary metal oxide semiconductors (CMOS) will face severe performance and power consumption challenges.

Despite the introduction of high-k/metal gate (HKMG), the reduction of the equivalent gate oxide thickness (EOT) is still challenging in the short term. The integration of high-dielectric materials, while limiting the increase in gate tunneling current due to the narrowing of the bandgap, will also face challenges. The complete gate stack material system needs optimization to obtain the best device characteristics (power and performance) and reduce costs.

New device structures, such as multi-gate MOSFETs (MOSFETs) and ultra-thin fully depleted insulator-on-insulator (FD-SOI), will appear. One of the most challenging problems is that these ultra-thin metal oxides Thickness control of semiconductor field effect transistors (MOSFETs). Solving these problems should be done in parallel with circuit design and system architecture improvements.

Some high mobility materials, such as germanium and III-V elements, have been considered as an upgrade or replacement of silicon channels in CMOS logic applications. High dielectric metal gate dielectrics with low body traps and low power leakage, unpinned Fermi levels, and low ohmic contact resistance are major challenges.

2. Memory Device Dynamic Random Access Memory (DRAM) Challenges in feature size reduction, high-dielectric-medium applications, low-leakage access device design, and low-resistivity materials for bitlines and wordlines, Has a suitable storage capacitor. In order to increase the bit density and reduce the production cost, the driver of the 4F type cell requires a high aspect ratio and a non-planar transistor structure.

Flash memory has become a new driver for Front End Of Line (FEOL) technologies such as key size scaling, materials, and processing (lithography, erosion, etc.) technologies. In the short term, the continuous development of flash density depends on the thinning of the tunnel oxide layer and the degree of dielectric integration.

In order to ensure the charge maintenance and durability requirements, the introduction of high-dielectric materials will be necessary. With over 256 GB of 3-D NAND flash memory, it is still a daunting challenge to maintain cost-effective performance while ensuring multi-level cell (MLC) and certain reliability. New challenges include the evolution of new memory type manufacturing and new memory concepts such as magnetic random access memory (MRAM), phase change memory (PCM), resistive random access memory (ReRAM) and ferroelectric random memory Take memory (FeRAM).

3. High-performance, low-cost RF and analog/mixed-signal solutions driving CMOS technology (high dielectric and strain engineering) in wireless transceiver ICs and millimeter-wave applications may require maintaining device mismatch and 1/f noise Technology in an acceptable range. Other challenges include the integration of cheaper, high-density integrated passive components, MEMS with integrated active silicon and off-chip passive network technologies, and the development of low-cost non-silicon (GaN) devices.

As the power supply voltage decreases as the complexity of the chip and the operating frequency increase, the signal isolation of the digital and analog regions on the chip becomes more and more important. Noise reduction may require more innovations, such as technical design to solve the power supply and grounding problems of high-resistivity substrates of the kilo-ohm level.

Many material orientations and structural changes, such as multi-gate and insulator-on-silicon (SOI) attenuation in the digital roadmap, or in turn alter RF and analog device behavior. There are complex trade-offs in optimizing RF, high frequency, and AMS performance, as well as the steady decline in supply voltage, which poses significant challenges for integrated circuit design.

4, 32, 22 nm half-pitch and lower lithography is becoming a very expensive and challenging technology. For 22 nm half-pitch lithography, 193 nm immersion lithography using spacer lithography or multiple modes will be used to overcome the limitations of the single mode, but with a very large mask error enhancement factor (mask). Error enhancement factor (MEEF), line edge roughness (LER), design rule limits, and higher cost. The wavelength of 13.5 nm Extreme-UV lithography (EUVL) is the industry's official desire to promote Moore's Law.

The challenge of deep UV lithography is the lack of delays due to high power sources, high-speed photoresists, and flawless, high-flat masks. Further challenges include increasing the numerical aperture of the deep ultraviolet system to over 0.35 and increasing the possibility of increasing the number of mirrors in the imaging system.

Multiple-e-beam maskless lithography has the problem of bypassing masks, removing the limitations of design rules, and providing the potential for manufacturing flexibility. Progress has been made in displaying high resolution images and CD control. The timing of manufacturing tools, cost, know-how, accurate overprinting, and photoresists are other fields that need further development.

Direct Self-Assembly (DSA) technology has made new progress, but its accuracy and positioning accuracy need to be improved.

Other challenges include gate length CD control and suppression of light-emitting resistors (LER) in lithography and etching, new gate materials, non-planar transistor structures, photoresist resistors, and deep ultraviolet Photolithography measurement.

5. Introduction of new materials Since low-dielectric materials (including porous materials and air gaps) must have sufficient mechanical strength to withstand cutting, encapsulation, and assembly, etch- and chemical-mechanical polishing (CMP) processes are considered to be low. The reduction in dielectric damage of dielectric materials has become more important. On the metal side, ultra-thin, conformal low resistivity barrier metals need to be integrated with copper to achieve low resistivity and high reliability.

6, power management Most applications, power management is the most important issue nowadays. Because the number of transistors per generation will increase exponentially, the cost-effective thermal performance of the packaged chips remains almost unchanged. In order to maintain system activity and reduce leakage power consumption, the realization of the corresponding circuit technology will be extended to the requirements of system design, improvement of computer aided design (CAD), reduction of leakage power consumption and performance requirements of new device architecture. .

(B) Short-term challenges (now up to 2020): Cost-effectiveness 1. Lithography Although deep-UV lithography with a wavelength of 13.5 nm is the official target of the industry, deep ultraviolet lithography must achieve very high source power to reach 10 nm. At a level above and above the technology is cost-competitive. Multi-beam maskless lithography may be the most economical option if it can maintain per-pass exposure, process cost, and traces similar to those of mask-based exposure tools. After introducing a smaller number of masks in the process, the digital storage architecture (DSA) of the 193 nm immersion lithography machine became very popular.

2. Front-end process We need to achieve low parasitic effects, continue to reduce the gate spacing, area adjustment of the next-generation substrate (adjusted to 450 mm wafers), and adopt breakthrough technologies to meet the lithography challenge.

3. The challenges faced by plant integration mainly include: firstly, responding to rapidly changing and complex business demands; secondly, increasing the complexity of managing factories; third, achieving economic growth while reducing marginal benefits; and fourth, meeting factories and equipment. Requirements for reliability, functionality, efficiency, and cost; Fifth, cross-border use of factory integration technologies, such as 300 mm and 450 mm, to achieve economies of scale; and 6 to address the unique challenges of migrating to 450 mm wafers.

4. Meeting the ever-changing cost requirements of the market Assembly and packaging challenges include 3D integrated chip stacking (testing: access, cost and known good chips, 3D packaging and packaging, test access to individual wafers or chips).

5. Challenges in the areas of environment, safety and health, environmental safety and health are: management and efficiency of chemicals and raw materials; process and equipment management; technical requirements for facilities; product management; reuse/recycling/reproduction of end-of-life products.

6. Measuring plant-level and company-level measurement integration: Measurements should be carefully selected and sampling must be statistically optimized to meet the cost of ownership (CoO) based on the owner's cost.

(III) Long-term challenges (2021 to 2028): Performance improvement 1. Implementation of atypical complementary metal oxide semiconductor channel materials provides sufficient drive current for highly miniature metal oxide semiconductor field effect transistors (MOSFETs) with enhanced heat The speed and quasi-ballistic operations injected at the source seem to be necessary. Therefore, high-speed transmission channel materials, such as III-V compounds or narrow channels of germanium on silicon substrates, and even semiconductor nanowires, carbon nanotubes, graphene, or other materials, are yet to be developed. Atypical complementary metal oxide semiconductor (CMOS) devices need to be physically or functionally integrated on a CMOS platform. This integration requires the epitaxial growth of foreign semiconductors on a silicon substrate, which is challenging. Ideal material or device performance must be maintained after high temperature and corrosive chemical processing. In the early days of technology development, reliability issues should be established and resolved.

Metal Table Lamp, the whole is mainly made of metal materials, suitable for bedroom, living room, office, study and other indoor places. Modern and simple design, diverse modeling, whether placed in the home or office, can be well integrated into the environment, suitable for decoration joker. Made of metal, it doesn't look bulky, and the overall line looks very smooth. In addition to playing the role of lighting, in the case of decorative space effect, whether the light is on, or off, is a work of art.

Metal Table Lamp

Golden Table Lamp,Big Metal Lamp,Black Metal Table Lamp,Brass Table Lamp

JIANGMEN LEDERLIGHT LIGHTING Co.,LTD , https://www.lederlightcn.com